產(chǎn)品與解決方案/PRODUCT AND SOLUTIONS

少用電 用好電 再生電 存儲(chǔ)電 防爆電

解決方案

反向整流同步信號(hào)模擬電路的獲取探討

引言

在反向整流控制中,需要6個(gè)控制IGBT的同步信號(hào),,在以前的試驗(yàn)中,,同步信號(hào)的獲取是先由模擬電路對(duì)兩個(gè)線(xiàn)電壓進(jìn)行調(diào)理,然后兩個(gè)線(xiàn)電壓信號(hào)再進(jìn)入DSP通過(guò)AD轉(zhuǎn)換為數(shù)字信號(hào)進(jìn)行處理,數(shù)字信號(hào)處理中又通過(guò)鎖相環(huán)或者帶通濾波處理得到正弦同步信號(hào),,最后通過(guò)這兩個(gè)正弦信號(hào)進(jìn)行適當(dāng)?shù)倪壿嬏幚淼玫?個(gè)控制IGBT的同步信號(hào),,在這種同步信號(hào)的獲取中硬件電路需要有DSP或者M(jìn)CU處理器來(lái)處理,涉及到這類(lèi)信號(hào)處理器就要考慮其可靠性,,如抗干擾方面,、PCB板布局方面、芯片多管腳的焊接方面等,。

針對(duì)上述情況,,我們考慮是否能直接用部分模擬電路簡(jiǎn)單產(chǎn)生信號(hào),然后通過(guò)CPLD進(jìn)行邏輯處理得到6個(gè)同步信號(hào),,在單元控制板中,,由于逆變也需要利用CPLD來(lái)處理逆變部分的信號(hào)和與主控進(jìn)行通信的處理,所以CPLD是必不可少的,,因此由模擬電路產(chǎn)生的信號(hào)通過(guò)CPLD處理也是比較直接的過(guò)程,。

1、存在的問(wèn)題

在模擬電路產(chǎn)生信號(hào)中,,主要還是對(duì)線(xiàn)電壓或者相電壓過(guò)零點(diǎn)的獲取,,在過(guò)零點(diǎn)的獲取中常用的是用運(yùn)放進(jìn)行過(guò)零比較。在反向整流工作中,,由于電源的內(nèi)阻存在,,在輸入電源上就存在IGBT開(kāi)通或關(guān)斷時(shí)產(chǎn)生的缺口,如圖1所示:

圖1,、反向整流工作的電源相電壓

上圖為反向整流工作時(shí)的電源相電壓,,對(duì)此如果用線(xiàn)電壓獲取同步信號(hào)時(shí)就會(huì)存在線(xiàn)電壓過(guò)零點(diǎn)的不準(zhǔn)確,如果對(duì)線(xiàn)電壓進(jìn)行濾波處理雖然可以去掉缺口,,但可能對(duì)信號(hào)產(chǎn)生相移,,從而用線(xiàn)電壓進(jìn)行比較獲取過(guò)零點(diǎn)并不大合適;如果用上圖相電壓進(jìn)行過(guò)零比較來(lái)獲取過(guò)零點(diǎn),,這樣在缺口處和過(guò)零點(diǎn)處就出現(xiàn)過(guò)零點(diǎn)信號(hào),,由于缺口處的寬度比較窄,缺口處可以通過(guò)CPLD處理去除,,然后留下比較真實(shí)的過(guò)零點(diǎn),,但是由于變壓器到單元之間為三相三線(xiàn)制,不存在中線(xiàn),,所以需要通過(guò)三相制造一個(gè)中點(diǎn),,但這樣這個(gè)中點(diǎn)的電位是不確定的,是浮動(dòng)的,,所以也完全可能造成過(guò)零點(diǎn)不準(zhǔn)確,,特別是三相出現(xiàn)不平衡時(shí)就比較明顯,,對(duì)此采用相電壓進(jìn)行過(guò)零比較也是不大合適。

2,、解決的方法

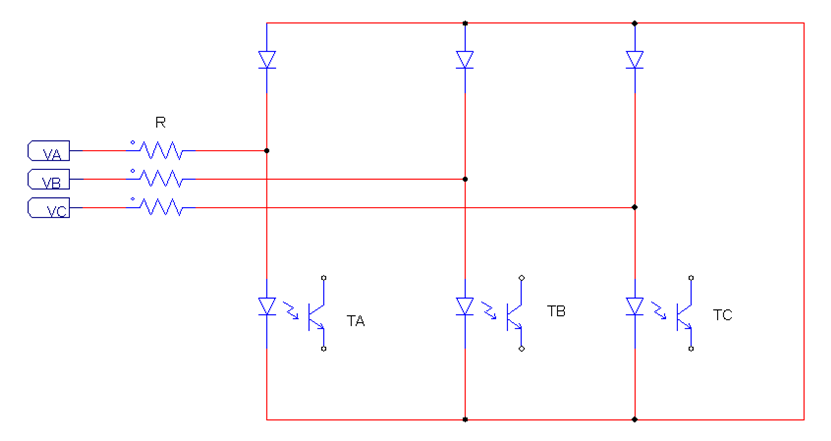

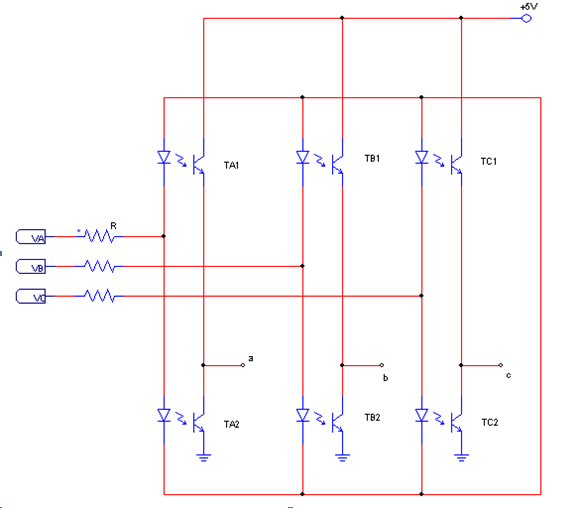

對(duì)于上述情況考慮采用光耦來(lái)獲取同步信號(hào)的過(guò)零點(diǎn),,這樣就可以不用考慮三相中點(diǎn)電位問(wèn)題,又能夠獲取相電壓的過(guò)零點(diǎn),,初步方式如圖2所示:

圖2,、光耦獲取同步信號(hào)

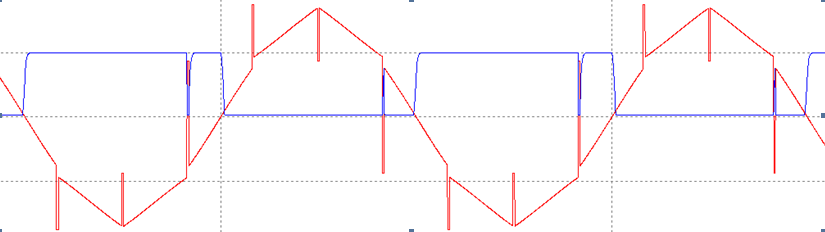

在這個(gè)電路中通過(guò)光耦TA、TB,、TC的次級(jí)就可以獲取三相的過(guò)零信號(hào),,但在反向整流工作中仍然由于電源缺口在光耦次級(jí)會(huì)有比較窄的過(guò)零脈沖,但是完全可以通過(guò)CPLD適當(dāng)?shù)奶幚砣サ?,如圖3中的藍(lán)色,,沒(méi)有經(jīng)過(guò)CPLD處理時(shí)獲取的信號(hào):

圖3、過(guò)零脈沖的獲取

3,、6個(gè)同步信號(hào)的產(chǎn)生方法

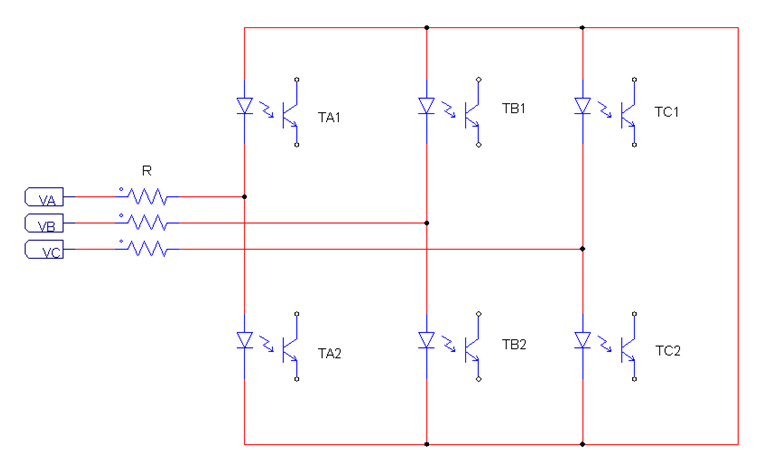

由于反向整流要求同步信號(hào)有比較高的對(duì)稱(chēng)波形,,上面的電路中只是取到了相電壓的大于零的部分,但由于光耦和二極管的壓降存在,,可能會(huì)使得不對(duì)稱(chēng)的情況產(chǎn)生,,所以如果要正負(fù)半周對(duì)稱(chēng),可以考慮使用6個(gè)光耦來(lái)產(chǎn)生信號(hào),,如下圖:

圖4,、6路同步信號(hào)的獲取電路

通過(guò)6個(gè)光耦就可對(duì)稱(chēng)地獲取三相的同步信號(hào),這6個(gè)同步信號(hào)先進(jìn)行整形,,然后進(jìn)入CPLD進(jìn)行窄脈沖的去除,,在去除窄脈沖時(shí),可以考慮利用延時(shí)的方法,,延時(shí)時(shí)間選擇為1.66667mS(對(duì)應(yīng)50HZ時(shí)的30度),,這樣既去除了窄脈沖又得到了線(xiàn)電壓的過(guò)零點(diǎn)信號(hào),然后對(duì)這6個(gè)信號(hào)進(jìn)行邏輯運(yùn)算就可得到驅(qū)動(dòng)6個(gè)IGBT的信號(hào),,完成同步信號(hào)的獲取,。

4、電路的優(yōu)化

在考慮用普通光耦達(dá)到快速的電平翻轉(zhuǎn),,可采用光耦次級(jí)進(jìn)行推挽輸出的方式,,這樣可以加速電平翻轉(zhuǎn)和減小光耦產(chǎn)生的延時(shí),其電路結(jié)構(gòu)如下:

圖5,、推挽輸出的電路

通過(guò)這種電路后,,在光耦的次級(jí)不存在取樣電阻的選擇,對(duì)輸出的信號(hào)a\b\c在光耦導(dǎo)通時(shí)由于其與電源和地之間阻抗較小,,抗干擾又有進(jìn)一步的提高,,存在的問(wèn)題是在上光耦和下光耦都沒(méi)有導(dǎo)通工作時(shí),,信號(hào)a\b\c輸出是處于不確定電平狀態(tài),,在進(jìn)入整形之前需要通過(guò)電阻確定電平,,在CPLD內(nèi)處理的過(guò)程和邏輯仍然相同。這種電路工作中相互得到的信號(hào)如下:

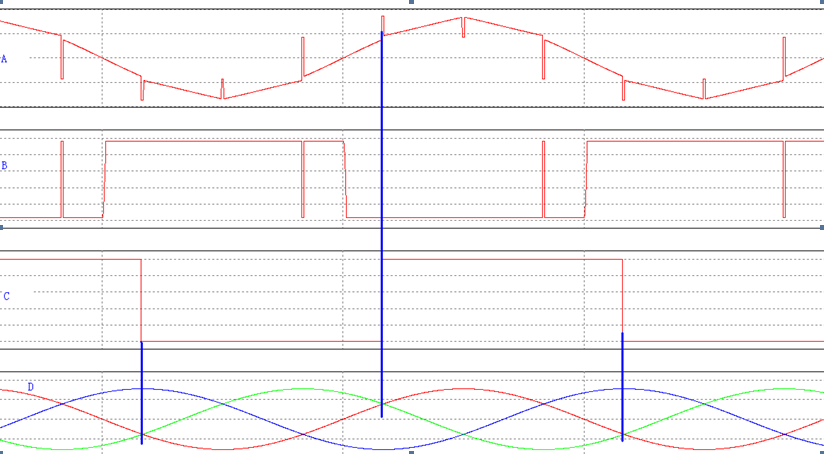

圖6,、電路的信號(hào)波形

A為a相的相電壓,,B為上電路結(jié)構(gòu)中a輸出的信號(hào),C為信號(hào)a進(jìn)行1.66667毫秒的延時(shí)濾波(圖中考慮光耦次級(jí)連接方式進(jìn)行了反向處理)波形,,D為理想中對(duì)應(yīng)的三相相電壓波形(三相相序?yàn)檎蚯闆r,,即B相滯后A相120度,C相滯后B相120度),,從波形上不難看出,,信號(hào)a進(jìn)行30度的濾波延時(shí)后其上升沿正好是線(xiàn)電壓AB的過(guò)零點(diǎn)(即A相與C相的交點(diǎn),見(jiàn)上圖中的D圖),,信號(hào)a\b\c進(jìn)行同樣的處理后可以進(jìn)行如下邏輯處理來(lái)得到6個(gè)驅(qū)動(dòng)信號(hào):

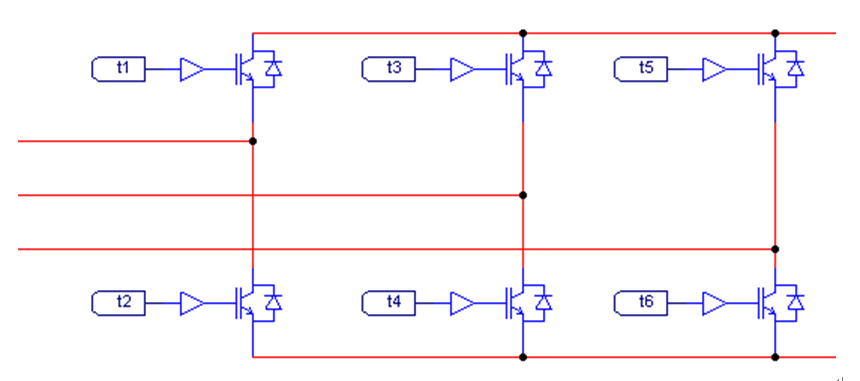

圖7,、信號(hào)的邏輯處理電路

圖中t1\t2對(duì)應(yīng)A相,t3\t4對(duì)應(yīng)B相,,t5\t6對(duì)應(yīng)C相,,假設(shè)信號(hào)a\b\c進(jìn)行濾波延時(shí)處理后的信號(hào)為A\B\C,則6個(gè)驅(qū)動(dòng)信號(hào)的邏輯處理為:

t1 = A and !B t2 = !A and B

t3 = B and !C t4 = !B and C

t5

= C and !A t6 = !C and

A

這樣邏輯處理后正好對(duì)應(yīng)6個(gè)IGBT是進(jìn)行120度工作,,在實(shí)際中CPLD內(nèi)還需要對(duì)輸入的三個(gè)信號(hào)進(jìn)行相序的辨識(shí),,上面的邏輯關(guān)系是對(duì)于正序A-B-C的關(guān)系,如果是負(fù)序(A-C-B)時(shí),,需要對(duì)邏輯關(guān)系進(jìn)行適當(dāng)調(diào)整,,負(fù)序時(shí)只需要將用到B相的信號(hào)與C相進(jìn)行交換即可。

5,、注意的問(wèn)題

在信號(hào)濾波延時(shí)過(guò)程中需要注意事項(xiàng),,由于光耦前級(jí)限流電阻不能選擇太小(電阻功率受限),,由于電阻值比較大,,在光耦次級(jí)產(chǎn)生的信號(hào)a\b\c存在延時(shí)問(wèn)題,電阻越大延時(shí)就越大,,此時(shí)在濾波延時(shí)的時(shí)間就要小于1.66667mS,,如果不減小延時(shí)時(shí)間,在回饋電流上就會(huì)產(chǎn)生比較大的峰值電流,,通過(guò)仿真可以看到,,如果R=500K時(shí),可以用濾波延時(shí)1.2mS時(shí),,峰值電流就比較小,,如果還用1.66667mS作為濾波延時(shí)時(shí),,峰值電流能達(dá)到正常電流的2倍以上。

在采用這種方法時(shí)利用電流觸發(fā)光耦導(dǎo)通,,從而可以提高抗干擾,,也不需要做AD變換來(lái)進(jìn)行數(shù)字處理,在單元輸入缺相時(shí),,其光耦產(chǎn)生的信號(hào)就不是180度導(dǎo)通的狀態(tài),,這樣就可利用CPLD進(jìn)行一個(gè)邏輯判斷就可知道是否缺相。

6,、總結(jié)

以上探討了直接用部分模擬電路簡(jiǎn)單產(chǎn)生信號(hào),,然后通過(guò)CPLD進(jìn)行邏輯處理得到6個(gè)同步信號(hào),去控制反向整流電路的方法,,實(shí)際應(yīng)用中也可能遇到?jīng)]有考慮全面的問(wèn)題,,需要在實(shí)際的試驗(yàn)中加以完善,但這畢竟是一個(gè)較好的控制策略,,比數(shù)字處理電路要來(lái)的簡(jiǎn)潔,、可靠,省去了抗干擾,、PCB板布局,、芯片多管腳的焊接等方面的困擾,應(yīng)該是一個(gè)較好的方法,。